## In Modul 1 enthalten:

- 1.1) Leiterplattenentwicklung einst ...

- 1.2) Hintergründe zur CAD unterstützten Leiterplattenentwicklung

- 1.3) Maßeinheiten mm / mil (Rastermaß)

- 1.4) Unsere Kriterien in der Leiterplattenentwicklung

- 1.4.1) Vorgaben zur PCB-Entwicklung

- 1.4.2) Design Rules! Die 6 Prüfungen für die Fertigung

- 1.4.3) Überblick der schulinternen Fertigung

© BAUW Seite 1 / 6

## 1.1) Leiterplattenentwicklung einst ...

In der Leiterplattenentwicklung unterscheidet man immer zwischen einem

- a) Schaltplan (oder Stromlaufplan) und der

- b) Leiterplatte (Entflechtung) selbst.

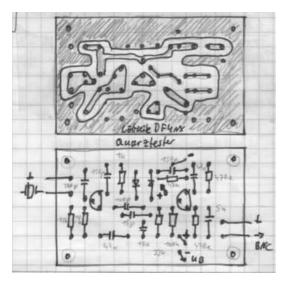

Bevor die CAD-unterstützte Leiterplattenentwicklung möglich wurde, mussten die Leiterplatten manuell auf einem Blatt Papier entflochten werden.

#### Was war dazu notwendig?

Natürlich mussten alle Bauteile zur Verfügung stehen, denn nur sie gaben Auskunft über die **Dicke des Anschlussdrahtes** (daraus ergibt sich der Lochdurchmesser), und die **Abmessungen des Bauteiles** (Bsp Elko: Aussendurchmesser und Pin-Abstand [Rastermaß]).

Aus dem Anschlussdraht musste auch der Paddurchmesser (Lötauge) abgeleitet werden.

Es war eine mühsame Arbeit, denn ständig wechselte des Werkzeug zwischen Bleistift und Radiergummi. Es war unmöglich, die Aufgabe in

einem einzigen Versuch zu lösen. Bei Fehlern oder Änderungen musste man von vorne beginnen. Hatte man es endlich geschafft, die Bauteile "vernünftig" zu platzieren und alle Verbindungen kreuzungsfrei zu verlegen, konnte man das Layout nun "produktionstauglich" umsetzen.

#### Hier gab es 3 Möglichkeiten:

- a) Klebetechnik: auf Rollen (wie Isolierband) gab es in unterschiedlichen Stärken "Leiterbahnen" in Meterware zu kaufen. Auch Lötaugen gab es als Klebevorlagen. Diese Elemente wurden auf eine Folie aufgebracht.

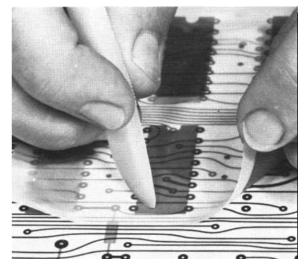

- b) **Rubbel-Technik**: Auch heute gibt es noch Leiterbahnen und Lötaugen als Rubbel-Symbole zu kaufen. Sie wurden auch auf eine Folie gerubbelt.

- c) **Edding**: Das Layout wurde direkt mit einem Stift auf das Basismaterial (Kupfer) gezeichnet.

© BAUW Seite 2 / 6

| Abt | Werkstatt |

|-----|-----------|

| EL  | Altıum    |

## Grundlagen der LP-Entwicklung

## 1.2) Hintergründe zu Leiterplattenentwicklungsprogrammen

Die beiden Elemente "Schaltplan" und "Leiterplatte" gibt es auch in Altium. Dort heißen sie "**Schematik-Dokument**" und "**PCB-Dokument**". PCB ist englisch und heißt "Printet Circuit Board" und bedeutet nichts anderes als "Gedruckte Schaltkreise".

Altium ist projektorientiert, d.h. dass alle Daten in einem einzigen File (dem Datenbankfile "name.prjpcb") abgelegt werden.

| Schaltplan           | Entflechtung                           |

|----------------------|----------------------------------------|

| = Schematik Dokument | = PCB Dokument (Printed Circuit Board) |

Im Schaltplan sind die Bauteilsymbole und Verbindungen (Netze) der einzelnen Symbole eingezeichnet.

Im PCB werden die einzelnen Footprints (Bauformen) und die Verbindungsleiterbahnen dargestellt.

Vor jeder Entflechtung sollten die Bauteile bereits organisiert werden, um Auskunft über die Bauform der Bauteile zu erhalten.

Die Bauform (=Footprint) beinhaltet:

- den Durchmesser der Anschlussdrähte und somit den Lochdurchmesser

- 2) den Paddurchmesser

- 3) das Rastermaß des Bauteiles

- 4) sowie die Abmessungen des Bauteiles (z.B. Durchmessser bei Elko)

All diese Informationen sind in den Altium Libraries (=Bauteilsammlung) bereits enthalten.

Update PCB

Footprint

© BAUW Seite 3 / 6

| Abt | Werkstatt |

|-----|-----------|

| EL  | Altıum    |

# Grundlagen der LP-Entwicklung

Wie jedes andere Leiterplattenentwicklungs-Tool arbeitet auch Altium mit sog. Netzen.

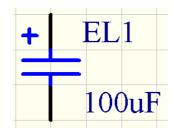

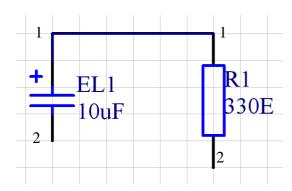

Jedes Bauteilsymbol (Schematik) besteht aus lebenswichtigen "**Pins**" und elektrisch unrelevanten **Zeichnungselementen**. Diese Pins sind die schwarz dargestellten Anschlüsse, welche einfach durchnumeriert sind.

Mit Hilfe dieser Pin-Nummern merkt sich Altium, welcher Pin zum Beispiel des Symbols EL1 mit welchem Pin des R1 verbunden ist.

Dieser Verbindung wird auch ein eigener Netzname zugewiesen.

Für Altium würde es also ausreichen, nur die Pins ohne den blauen Zeichnungselementen zu platzieren. Natürlich ist der "Schaltplan" dann für uns Menschen nicht lesbar.

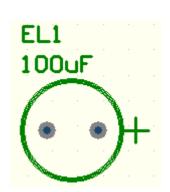

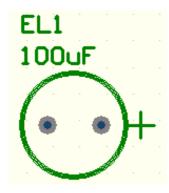

Auch die sog. "Footprints" (= Fußabdruck) beinhalten Pins. Hier sind es die grauen PAD's, die ebenfalls durchnumeriert sind und zusätzlich über den Bohrdurchmesser und den Lötaugendurchmesser Auskunft geben.,

Betrachten wir nebenstehenden Footprint, so muss bereits jetzt klar sein, wo Pin1 und wo Pin2 ist!

Richtig, Pin1 ist rechts, da im Symbol (siehe oben) das Plus-Zeichen bei Pin1 ist.

Sollten die Pins im Footprint falsch numeriert sein (zB. mit 2 und 3), so meldet Altium einen Fehler bei "Update PCB" (dazu später), da das Netz, welches in der Schematik mit dem Pin1 verbunden ist, dem Footprint nicht zugewiesen werden kann.

© BAUW Seite 4 / 6

## 1.3) Maßeinheiten mm / mil (Rastermaß)

Euch ist sicher schon aufgefallen, dass auf euerem Steckbrett die Kontakte immer im gleichen Raster angeordnet sind. Bei einer Lochrasterplatine sind die Löcher in der Platine im selben Raster angeordnet. Den Abstand von Kontakt zu Kontakt nennt man Rastermaß.

Wie groß schätzt ihr diesen Abstand? 5mm? 1mm? 3mm? Messt doch mal mit dem Lineal nach!

Wie bitte, ich messt 2,5mm? Ja, fast richtig!

Das korrekte Rastermaß ist mit dem Lineal nicht messbar – **2,54mm** sind es.

Wie kommt die Menschheit auf dieses verrückte Maß?

Dieses Maß hat seinen Ursprung im englischen Zoll oder Inch.

1 ZoII = 1 inch = 2,54cm = 25,4mm

Wird bei einem Monitor oder einem Fernsehgerät nicht auch die Bildschirmdiagonale (= sichtbares Bild, ohne Rahmen des Gerätes) in Zoll angegeben?

## Richtig!

Bsp:

Diagonale = 24" x 25,4cm = 60,9cm

1 inch lässt sich (so wie 1kg in 1000g) auch in 1000 mil zerteilen.

#### Also:

1 inch = 1 Zoll = 1000mil = 2,54cm = 25,4mm

1 inch = 1000mil = 25,4mm ... nun alles geteilt durch 10

1/10 inch = 100mil = 2,54 mm

#### MERKE:

100mil = 2,54mm = 1 Rastermaß

#### Merke auch:

100mil = 2,54mm | 10mil = 0.254mm | 20mil = 0.508mm | 30mil = 0.762mm 40mil = 1.016mm | 50mil = 1.27mm

© BAUW Seite 5 / 6

## Grundlagen der LP-Entwicklung

## 1.4) Unsere Kriterien in der Leiterplattenentwicklung

#### 1.4.1) Vorgaben zur PCB-Entwicklung:

- o) PCB so klein wie möglich (oder an Vorgabe/ Gehäuse angepasst)

- o) Bauteilanordnung so kompakt wie möglich

- o) so wenige Lötpunkte wie möglich (Lochraster)

- o) so wenige Leitungen wie möglich (Lochraster)

- o) so kurze Leitungen wie möglich / sinvoll

- o) Leiterzugsecken mit 90° verlegen (bei händischer Entflechtung am Papier)

- o) Leiterzugsecken mit 45° verlegen (Altium)

In Altium können wir auch Design-Regeln hinterlegen und nach Fertigstellung der Entflechtung mit dem Design-Rule-Check überprüfen, ob wir diese auch eingehalten haben. Die wichtigsten Regeln (Rules) sind:

#### 1.4.2) Design Rules! Die 6 Prüfungen für die Fertigung:

o) Abstand von Kupfer zu Kupfer

Clearance: CU zu CU = 0.38mm CU zu Fläche = 0.75mm

o) Stärke der Leiterzugsbreiten

Routing Width: min. 0.4mm; bevorzugt 0.75mm

o) Anbindungen an Kupferflächen (Wärmefallen)

Polygon Connect: Air Gap und Conductor jeweils 0.5mm

o) Restring = (Padgröße - Lochdurchmesser)/2

Minimum Annular Ring: 0.5mm

o) Kurzschlüsse

Short-Circuit (nur aktivieren)

o) Unterbrechungen / nicht verlegte Leitungen

Un-Routed-Net (nur aktivieren)

## 1.4.3) Überblick der schulinternen Fertigung:

- o) größte Platinenabmessungen: so, dass der Layoutausdruck noch auf ein Blatt A4 passt

- o) die kleinste Bauteilbohrung = 0.75mm

- o) der dünnste zu ätzende CÜ-Strich = 0.4mm (egal ob Leiterzug, Konturlinie, Schrift ....)

- o) der kleinste Restring = 0.5mm

Ausnahmen bitte vorab mit mir absprechen lassen!

© BAUW Seite 6 / 6